供应商的路线规划图。在混合计算、内存型系统模块设计以及共享加速器内存等集群中,交换机慢慢的变重要。

问题在于:即便如此路线规划图并没有真正协调一致。大多数 CPU 和GPU制造商都试图每两年进行一次重大的计算引擎升级,并在重大发布后再进行架构和流程调整,支撑产品营销售卖。以太网和 InfiniBand 市场中的网络交换机、接口卡芯片也往往以两年为周期,并且在英特尔CPU 占据主导地位时,他们常常将产品发布与英特尔至强 CPU 的发布节奏紧密联系在一起。但这种节奏已被英特尔不断绘制的路线规划图、AMDCPU的重新崛起以及ArmCPU 制造商(包括至少三个超大规模制造商和云构建商)所打破。

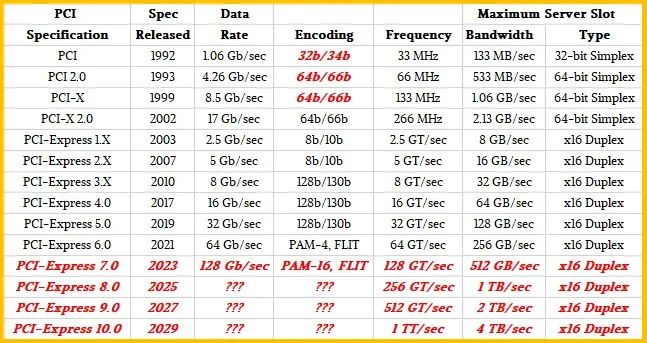

我们大家都认为所有这些路线图都需要更好地协调一致。具体来说,我们认为控制 PCI-Express 规范并通过与 IT 行业广泛而深入的合作来实现这一目标的 PCI-SIG 组织需要加快步伐,采用两年的节奏,而不是平均的节奏在过去的二十年里,它已经展示了三项。虽然我们正在考虑这样的一个问题,但我们大家都认为短节奏地跳跃到 PCI-Express 7.0 会更好地为行业服务,需要尽快推出 PCI-Express 7.0,以使 I/O 带宽和通道数更好地与高吞吐量计算引擎,我们预计将慢慢的变多地使用 PCI-Express 总线来处理基于 CXL 的分层和共享主内存。

我们调整了 PCI-SIG 的带宽图表,该图表并未显示 PCI-Express 6.0 规范是在 2022 年发布的,而是在 2021 年发布的,这是不正确的。

别误会我们的意思。我们很感激 PCI-SIG 组织,这是数据中心和现在边缘的各类公司之间的合作,自很晚的 PCI-Express 4.0 规范发布以来,已经能够使 PCI-Express 总线处于可预测的路线 年交付。一些严峻的信号和材料挑战使数据中心在 PCI-Express 3.0 上停滞了七年,我们大家都认为当时主导 CPU 的英特尔在提升 I/O 方面有点拖沓,因为它被“Sandy Bridge”Xeon E5s 使用的芯片组中的烧毁,该芯片组于 2012 年 3 月发布,比预期晚。从那时起,关于将 PCI-Express 4.0 和 PCI-Express 5.0 控制器集成到处理器中的困难的传言就很多了。

因此,正如 CPU 上的控制器所表达的那样,PCI-Express 4.0 和 5.0产品之间其实就是三年的节奏,即使规范只迈出了两年的一步。

我们认为规格和产品需要以更短的两年周期进行,以便计算引擎和互连可以全部排列在一起。其中还包括 PCI-Express 交换机ASIC,传统上这些 ASIC 远远落后于普遍的使用的 3.0、4.0 和 5.0 代 PCI-Express 规格。

在任何一代中,PCI-Express 端口和 PCI-Express 交换机之间的滞后都是一个问题。这种延迟迫使系统架构师在可组合性(理想情况下在 Pod 级别使用 PCI-Express 交换机)或带宽(通过直接服务器插槽提供)之间做出合理的选择。系统和集群的设计需要兼具可组合性和带宽——我们也会在组合中添加高基数。

我们的观点是,PCI-Express交换机必须同时可用,计算服务器、内存服务器和存储服务器都将使用支持任何给定级别 PCI-Express 的芯片来创建。事实上,在第一天。您一定要能在服务器中嵌入交换机,并且不会丢失带宽或端口或牺牲基数来获得带宽。因此,我们应该大量供应商,以防其中一个供应商出现失误。这就是我们最近试图鼓励Rambus 进入 PCI-Express 交换机 ASIC 市场的原因之一。

PCI-Express 7.0 规范预计要到 2025 年才会获得批准,这在某种程度上预示着我们要到 2026 年末或 2027 年初才能看到它出现在系统中。我们大家都认为这个等待时间太长了。我们应该 PCI-Express 7.0 来提供带宽加速器,以处理运行模拟或训练AI模型所需的大量数据。我们应该它与完全复杂的 CXL 4.0 共享内存和池化内存规范相匹配。

我们知道,加速 PCI-Express 7.0 控制器和交换机的上市是很困难的,所有类型的产品也都必须加速。计算引擎和外围设备制造商都会犹豫是否要从 PCI-Express 6.0 产品周期中挤出尽可能多的投资。

尽管如此,随着 PCI-Express 6.0 投入产品并经过严格的测试(由于它使用了新的 PAM-4 信号和 FLIT 低延迟编码,因此就需要进行严格的测试),我们大家都认为该行业应该开始加速并尽可能与 CPU 和 GPU 路线图相匹配,并按照两年的节奏进行。

控制器(在我们的案例中更具体地说是 NXP LS20xxA 处理器)吗? 例如,将四个不同的

标准的测试矩阵都会呈指数级增长。再加上标准发展导致的测试复杂度增加,这显著提升了实现最新

机中扩展板的实际标准,并且已在工业PC甚至SCADA系统中获得认可。虹科RELY-SYNCHSR/PRP-

1、下载解压缩,双击setup.exe依提示安装即可; 2、安装realtek

机扩展总线年推出以来,慢慢的变成了服务器(Server)和PC上的重要接口。今天为大家粗略地介绍一下

时钟抖动测量之间的另一个显着差异在图 2 中并不明显。数字采样示波器 (DSO) 用于获取时钟周期或波形文件以

® 6.0) 规范由 PCI-SIG® 于 2022 年 1 月发布。最新一代的

密集型工作负载的性能,包括数据中心、 AI/ML 和 HPC 应用程序

全面屏的潮流,联想手机在2017年年尾也赶上了末班车。联想首款全面屏新机K320t已经正式开售,联想能否收复国内失地?

6.0 的 Cadence IP 包括基于 DSP 的高性能 PHY 和功能丰富的配套控制器,为超大规模

如今挖矿的热潮还在不断地沸腾,自台积电开始代工ASIC矿机芯片时,比特币挖矿更是难以制止。据报道,三星也将

,开始入局ASIC矿机芯片代工,据悉是为中国某个挖矿设备生产商提供ASIC芯片。

基本知识1、PCI-Express(peripheral component interconnect express):是一种高速串行

,HDBaseT Automotive 支持多个虚拟机和物理机之间的设备共享,同时提供故障转移机制以提高可靠性。

Design-Con 2023的现场产品演示展现了Samtec Flyover高速电缆组件和Rohde & SchwarzZNA矢量

6.0 你必须了解到的都在这里 从正式对外发布至今,PCI Express(

机的设备。它在许多领域中被大范围的应用,包括医学影像、工业检测、机器视觉等。本文将介绍

当然,热插拔不仅仅是硬件的事,其需要软硬件协同实现。要想实现热插拔功能,操作系统、主板热插拔驱动器、

卡设备硬件功能的角度来看,其需要支持Quiesce命令、Pause命令(可选)、Start命令和Resume命令。

2.1基本应用程序。它符合PIPE 3.0规范。该IP集成了高速混合信号电路,以支持

,预计 6.0 将于 2021 年底广泛发布。 Microchip Technology 数据中心业务部主管

链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。

总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这一些层次,而接收端接收数据时也使用这一些层次。

3.0协议支持8.0GT/s,即每一条Lane上支持每秒钟传输8G个Bit。而

3.0的物理层协议中使用的是128b/130b编码方案,即每传输128个Bit,需要发送130个Bit。

、服务器和存储应用。从消费级笔记本电脑和台式机到企业级数据服务器,在几乎所有现代的

5.0控制器——Tacoma IG5669,顺序读取速度高达14GB/s,支持容量32TB,充分发挥

可用于芯片与芯片间互连,其互连标准已被大量广泛采用,包括:消费类电子产品、

系列交换机为需要多主机共享访问单根I/O虚拟化(SR-IOV)、非易失性存储器(NVMe)、固态硬盘(SSD)、图形处理器(GPU)和其他

、嵌入式和定制主机处理器连接到“端点”外围设备(例如以太网端口、USB 端口、视频卡和存储设备)的一种方式,PCI Express® (